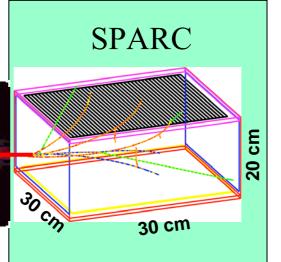

# actar

# ACTAR workshop - June

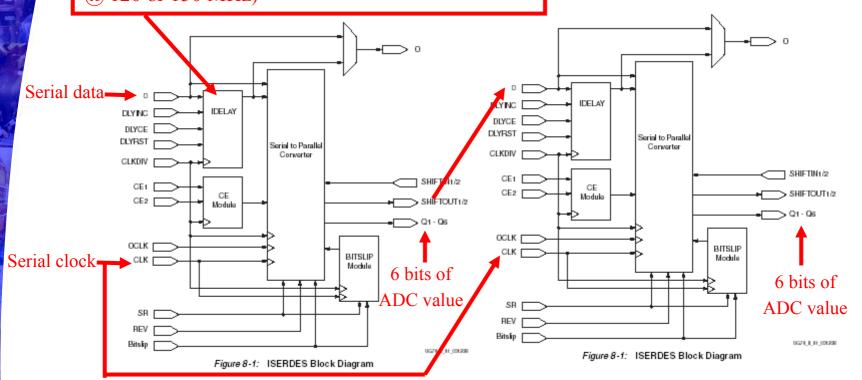

## About data alignment & Deserializer

64-tap delay element: Tidelay\_resolution ≈ 74ps So 63\*74ps, up to 4.66 ns (more than half a period (a) 120 or 150 MHz)

### in Xilinx FPGA

Input Serial-to-Parallel Logic Resources (ISERDES)

2 ISERDES to convert the high speed data stream from the ADC (150 Mbit/s) to 12 bits parallel value

The Virtex-4 FPGA ISERDES is a dedicated serial-to-parallel converter with specific clocking and logic features designed to facilitate the implementation of high-speed sourcesynchronous applications. The ISERDES avoids the additional timing complexities encountered when designing desertalizers in the FPGA logic.

**Xilinx Press Release**

http://www.xilinx.com/prs rls/2007/silicon vir/0760 v4adc.htm and application note @

Global architecture proposal

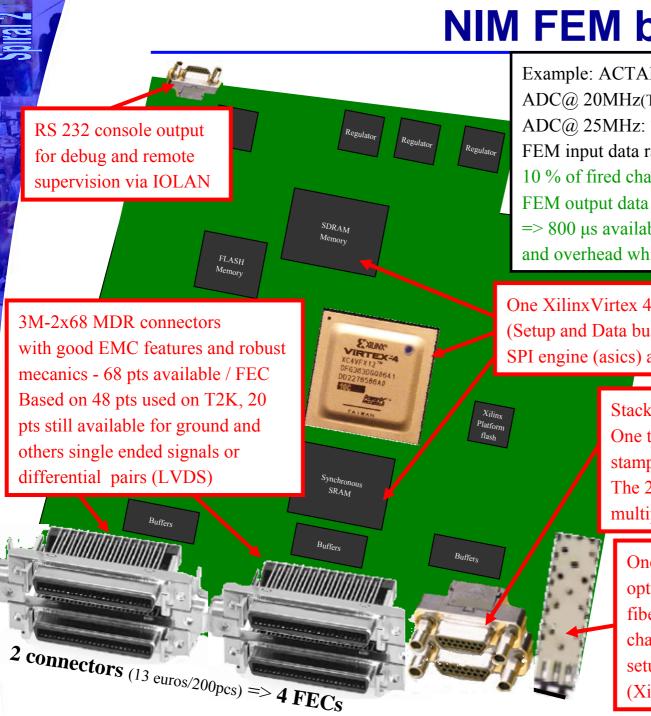

## **NIM FEM board details**

Example: ACTAR @GANIL

ADC@ 20MHz(T2K): 72 x 511 x 50ns  $\approx$  1.839 ms

ADC@ 25MHz: 72 x 511 x 40ns  $\approx$  1.47ms

FEM input data rate 4 x 300 Mbit/s (12bits/25 MHz)

10 % of fired channels: Tconv. = 147  $\mu$ s

FEM output data rate @ 1Gbit/s: Ttransfer  $\approx 50 \mu s$

=> 800 µs available for data treatment (zeros sup.) and overhead while keeping 1KHz of counting rate.

One XilinxVirtex 4 FX with enough external memory (Setup and Data buffers) with at least 1 processor for SPI engine (asics) and board supervision

> Stacked 15 pts Micro D connector One to receive clock (100MHz), timestamp information, trig. val., ... The 2<sup>nd</sup> to transmit the digital multiplicity (ex: 6 bits/4 FECs)

One SFF (or SFP) Gbit optical coupler for duplex fiber used as acquisition channel in TX way and setup/slow control in RX way (Xilinx-RocketIO)

**Gilles Wittwer**

NIM Back End Module Details

XilinxVirtex 4 FX (PPC405) with large external memory (TCP/IP stack

Internal reference clock (TCXO,VCXO)

Setup done through an

(4 Transmit channels + 4 Receive channels ) at the

ACTAR workshop - June 16

3579 euros / unit 2950 euros by 10 x 8 lanes all inclusive

+ 128 MB of DDR2 SDRAM

Based on XilinxVirtex 4 FX100 fpga with two PPC405 processors

Gilles Wittwer

## Xilinx V5 back end card details

3 duplex fibers

by PCIe board

via SFP

optical Gbit transceivers

New XilinxVirtex 5 FX70T fpga

with two PPC440 processors

+ 128 MB of DDR2 SDRAM

PCI Express

2.0 compliant

(5 Gb/s by lane)

9805 euros / unit 5200 euros by 10

all inclusive

# ACTAR workshop - June 16-18 2008, Bordeaux

## **Conclusion**

### In terms of performances

- Input Counting Rate of 2 or 3 kHz seems reachable with 511 cells/ch with 10% of fired channels

- Worst case for a full readout is less than 500 Hz of ICR

- In terms of work (and manpower ...)

- Minimum of 5 boards to design (2 years/ board with hardware and firmware)

- Two types of FEC, one FEM, one MUTANT module and one BEM

- In terms of budget for a serial production (except the FEC)

- 9 FEMs : 9 x 2000 euros = 18000

- 1 MUTANT module 3000

- 1 BEM module 3000

- 1 NIM crate 5000

- 1 IOLAN 2000

- 2 PC (Setup & ACQ) 3000

- 3 PCI express boards (V4) = 9000

- Duplex fibers, cables ... 2000

TOTAL =  $45000 \text{ euros} \Rightarrow 4.5 \text{ euros/channel}$